PCB板是電子產品的必需品,沒有PCB板哪來的各種家電,網絡等.電子設備采用印制板后,由于同類印制板的一致性,從而避免了人工接線的差錯,并可實現電子元器件自動插裝或貼裝,自動焊錫,自動檢測,保證了電子設備的質量,提高了勞動生產率,降低了成本,并便于維修.同樣有PCB板沒有電子元器件一樣無用,該篇文章康比電子介紹關于PCB的設計問題.

PCB設計

我們希望使用PCB布局來最小化振蕩器和外部信號之間的耦合.高頻耦合將激發晶體的高次諧波.晶體是噪聲源,可能會干擾外部電路.

PCB布局規則#1-使晶體靠近微控制器

短跡線具有低互感和電容.長跡線具有高互感和電容.保持晶體靠近微控制器會縮短走線,從而減少耦合.

PCB布局規則#2-與高頻信號隔離

在路由非振蕩器信號時,請遠離石英晶體振蕩器電路.無論您放置跟蹤的哪個圖層,此規則都適用.

考慮使用一個保護環-一條帶有過孔的銅線,它圍繞著你的振蕩器電路.這將減少外部信號線和振蕩器之間的互感.圖2顯示了我在最近的設計中放置的一個.

圖1:兩種晶體的PCB布局

通常的做法是將振蕩器電路下方的接地平面分開.僅在一點處連接分離的接地層-緊鄰微控制器接地.這可以防止來自其他信號源的返回電流通過振蕩器使用的接地層.我在圖2的設計中也做到了這一點,但在圖像中并不明顯.

水晶選擇和權衡

選擇水晶時需要進行以下權衡:

●可推移性-衡量振蕩器對頻率變化的脆弱性

●能量消耗

●啟動時間-上電后達到穩定振蕩所需的時間

●包裝尺寸

●成本

權衡:可轉移性與功耗

具有低可牽引性的晶體需要更大的負載電容.電容器能量必須在每個振蕩周期中傾倒,因此較大的負載電容器意味著較高的功率損耗.許多微控制器數據表建議使用負載電容的最大值,以降低驅動電路的功耗.所以你需要權衡;穩健性或功耗.

只是為了澄清,這種權衡取決于所選晶體的CL要求;不是CL1和CL2值.如果需要降低功耗或提高可拉性,請選擇需要不同CL的新晶振.

權衡:啟動時間與包裝尺寸

較小的晶體封裝具有較大的ESR.較大的ESR會產生較大的臨界增益(gm_crit),從而降低增益裕度.增益裕度降低意味著晶體啟動時間更長.

交易,成本

有些水晶比其他水晶便宜.我想說價格較高的晶體意味著質量更好;但這有時只是真的.

就電容器而言,在皮法范圍內,C0G幾乎就是所有可用的.它們具有+/-5%的容差,適用于振蕩器電路.

讓我們為STM32F427設計一個8MHz晶體振蕩器電路.

第1步:選擇水晶

我們對水晶有什么耐受性?

STM32F427數據表指定了以下內容:

1.對于4-26MHz晶體,Gm_crit_max=1mA/V.

2.頻率容差必須為+/-500ppm或更高

3.CL1和CL2建議每個5pF到25pF

讓我們從TXC中選擇7A-8.000MAAJ-T.盡管STM32的引腳間距為0.5mm,石英晶振的小尺寸仍然可以讓它靠近STM32.

該晶體具有以下特性:

CL=18pF

ESR=60歐姆

頻率穩定性=50ppm

頻率容差=30ppm

C0=7pFmax

驅動電平=最大500uW

第2步:檢查微控制器是否可以驅動晶振

首先,計算gm_crit:

所以gm_crit低于Gm_critmax.振蕩器電路將可靠啟動.

第3步:SMD石英晶振可以處理功率損耗嗎?

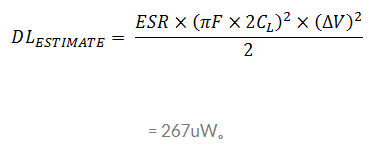

接下來,粗略估計電路的驅動電平:

計算出的驅動電平低于晶振的最大允許驅動電平500uW.

步驟4:選擇負載電容CL1和CL2

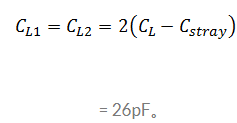

假設,雜散=5pF的(對于STM32應用手冊AN2867建議此作為初始估計),則:

STM32石英晶體振蕩器建議將CL1和CL2保持在25pF以下.供應商僅庫存24pF和27pF電容器;不存在26pF電容.選擇24pF或27pF電容就可以了.